# ANALOG-DIGITAL CONVERSION

# Walt Kester Editor

ANALOG DEVICES

. . . . .

FUNDAMENTALS OF SAMPLED DATA SYSTEMS 2.3 DATA CONVERTER AC ERRORS

The effects of aperture and sampling clock jitter on an ideal ADCs SNR can be predicted by the following simple analysis. Assume an input signal given by

$$v(t) = V_0 \sin 2\pi ft \qquad Eq. 2.29$$

The rate of change of this signal is given by:

$$dv/dt = 2\pi f V_0 \cos 2\pi f t$$

. Eq. 2.30

The rms value of dv/dt can be obtained by dividing the amplitude,  $2\pi f V_0$ , by  $\sqrt{2}$ :

$$dv/dt|_{ms} = 2\pi f V_0 / \sqrt{2}$$

. Eq. 2.31

Now let  $\Delta v_{rms}$  = the rms voltage error and  $\Delta t$  = the rms aperture jitter t<sub>j</sub>, and substitute:

$$\Delta v_{rms} / t_j = 2\pi f V_0 / \sqrt{2}$$

. Eq. 2.32

Solving for  $\Delta v_{rms}$ :

A

$$\Delta v_{rms} = 2\pi f V_0 t_j / \sqrt{2}. \qquad Eq. 2.33$$

The rms value of the full-scale input sinewave is  $V_0/\sqrt{2}$ , therefore the rms signal to rms noise ratio is given by

$$SNR = 20 \log_{10} \left[ \frac{V_O / \sqrt{2}}{\Delta v_{ms}} \right] = 20 \log_{10} \left[ \frac{V_O / \sqrt{2}}{2\pi f V_O t_j / \sqrt{2}} \right] = 20 \log_{10} \left[ \frac{1}{2\pi f t_j} \right].$$

Eq. 2.34

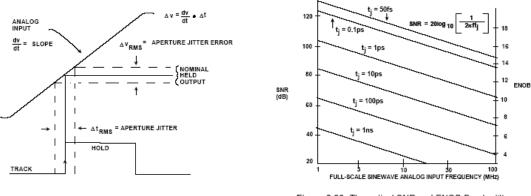

This equation assumes an infinite resolution ADC where aperture jitter is the only factor in determining the SNR. This equation is plotted in Figure 2.80 and shows the serious effects of aperture and sampling clock jitter on SNR, especially at higher input/output frequencies. Therefore, extreme care must be taken to minimize phase noise in the sampling/reconstruction clock of any sampled data system.

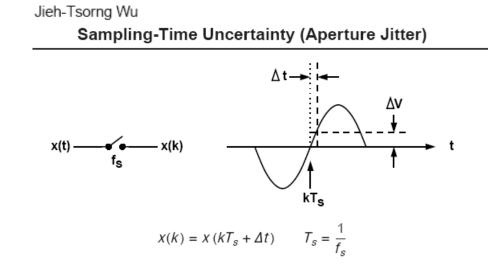

Figure 2.79: Effects of Aperture Jitter and Sampling Clock Jitter

Figure 2.80: Theoretical SNR and ENOB Due to Jitter vs. Fullscale Sinewave Input Frequency

Note: The effects of phase jitter on the external sampling clock (or the analog input for that matter) produce exactly the same type of error.

# **Clocking high-speed data converters**

By Eduardo Bartolome, High-Speed ADC Systems and Applications Manager (Email: e-bartolome1@ti.com), Vineet Mishra, High-Speed ADC Design Engineer (Email: vineetm@ti.com), Goutam Dutta, High-Speed ADC Test Engineer (Email: g-dutta2@ti.com),

and David Smith, High-Speed ADC Test Engineer (Email: w-smith13@ti.com)

### Introduction

In circuit design that involves the use of a high-performance, high-speed analog-todigital converter (ADC) such as the ADS5500, one of the main careabouts is the clocking scheme. Questions about the type of clock to be used (sinusoidal or square), the voltage levels, or the jitter are common. The purpose of this article is to explain the general theory to support the circuit designer in making the right choices.

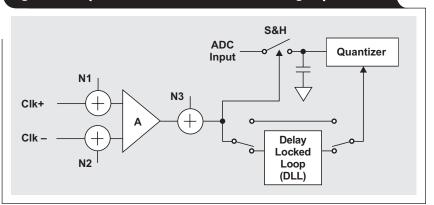

Figure 1 shows a simplified model of the clock circuit inside a high-speed ADC like the ADS5500. Although not all ADCs have exactly the same internal blocks in their clock distribution, this diagram can be

modified to fit your particular ADC. Since nowadays most of the circuits sold as ADCs include a front sample-and-hold (S&H), for the purpose of this article we will differentiate between them. The circuit that takes an instantaneous analog snapshot of the input signal will be called the S&H; and the ADC itself, which converts the analog value being held by the S&H into quantized digital output, will be called the quantizer. Analyzing what parameters of the internal clock are important for these two circuits will help us understand the main careabouts in our external clock design.

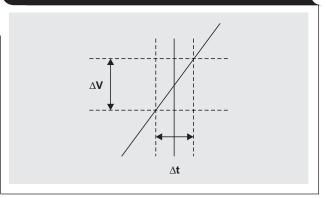

# Errors in the sampling instant

The conversion process starts when a clock signal tells the S&H to take the sample. Up to that instant, the internal switch on the S&H circuit has been closed, allowing the voltage across the capacitor to track the input signal (which is why other literature more properly calls this circuit "track and hold"). One of the edges of the input clock then indicates when to open this switch, and the capacitor holds the voltage at that instant in time. This instant is represented in Figure 2 by a vertical solid line. Any error in that instant ( $\Delta$ t) will translate as an error in voltage ( $\Delta$ V) dependent on the input signal slope. The error in that instant is what we will call jitter.

### Figure 1. Simplified model of clock circuit in high-speed ADC

A mathematical estimation of the best-case signal-tonoise ratio (SNR) (without other noise sources), given a certain amount of jitter, can be extracted from Figure 2. Given a sinusoidal input of amplitude A and frequency  $f_{\rm IN}$ (1/T), the uncertainty of the sampled voltage at a given point will be proportional to the slope of the input signal at that instant and to the uncertainty of the sampling instant (jitter, which is the rms value of that variation,

### Figure 2. Voltage error relation to sampling jitter

$$\begin{aligned} \sigma_{\text{Jitter}}^2 &= \frac{1}{T} \int_0^T \left( \text{Slope}(\tau) \times \text{Jitter} \right)^2 \mathrm{d}\tau = \frac{1}{T} \int_0^T \left[ \frac{\mathrm{d} \left( A \sin \frac{2\pi\tau}{T} \right)}{\mathrm{d}\tau} \text{Jitter} \right]^2 \mathrm{d}\tau \\ &= \frac{1}{T} \text{Jitter}^2 \int_0^T \left( \frac{2\pi A \cos \frac{2\pi\tau}{T}}{T} \right)^2 \mathrm{d}\tau = \left\langle a = \frac{2\pi\tau}{T}, \frac{\mathrm{d}a}{\mathrm{d}\tau} = \frac{2\pi}{T} \right\rangle \\ &= \frac{T}{2\pi} \left( \frac{2\pi A}{T} \right)^2 \text{Jitter}^2 \frac{1}{T} \int_0^{2\pi} (\cos^2 a) \mathrm{d}a = \frac{T}{2\pi} \left( \frac{2\pi A}{T} \right)^2 \text{Jitter}^2 \frac{1}{T} \frac{1}{2} (a + \sin a \times \cos a) \Big|_0^{2\pi} \\ &= \frac{T}{2\pi} \left( \frac{2\pi A}{T} \right)^2 \text{Jitter}^2 \frac{1}{T} \pi = \frac{1}{2} \left( \frac{2\pi A}{T} \right)^2 \text{Jitter}^2 \end{aligned}$$

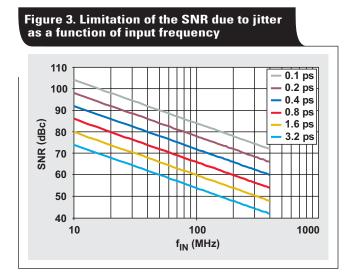

The theoretical limitation of the SNR due to jitter is given by

SNR (dBc) =

$$\frac{S}{N} = 10 \log_{10} \left[ \frac{\frac{A^2}{2}}{\frac{1}{2} \left(\frac{2\pi A}{T}\right)^2 \text{ Jitter}^2} \right] = -20 \log_{10} (2\pi f_{\text{IN}} \text{ Jitter}).$$

(1)

Figure 3 shows this limitation as a function of the input frequency.

Observe that increasing or decreasing the input amplitude  $(A_{IN})$  has no effect on the SNR component coming from jitter. In other words, as we decrease the input amplitude, the amount of error due to the jitter also becomes smaller. Nevertheless, there are other sources of error, like thermal noise, that do not get smaller. Assuming all these sources of noise are uncorrelated, the total noise is the addition of a noise term independent of input frequency and a noise term dependent on input frequency (jitter):

SNR (dBc) = 10log<sub>10</sub>

$$\left[ \frac{\left(\frac{A}{\sqrt{2}}\right)^2}{\text{Thermal + Quantization + }\frac{1}{2} \left(\frac{2\pi A}{T}\right)^2 \text{Jitter}^2} \right]$$

(2)

# Alfio Zanchi, and Frank (Ching-Yuh) Tsay, A 16-bit 65-MS/s ADC Core

#### • • • • •

The SNR limitation from jitter can be calculated via the classic formula

$$SNR_{jitter} = 10 \cdot \log_{10} \left( \frac{P_{IN}}{\sigma_V^2 j_{jitter}} \right)$$

$$= 10 \cdot \log_{10} \left( \frac{P_{IN}}{\frac{\sigma_T^2}{2} (A_{IN} \omega_{IN})^2} \right)$$

$$= -20 \cdot \log_{10} (2\pi f_{IN} \sigma_T)$$

(8)

a mathematical justification of which was published in [17]. Although intuitive, such a derivation is still heuristic. A more rigorous demonstration is found in the probabilistic theory, and for sake of clarity is reported in the Appendix

#### APPENDIX

In the following, we introduce a mathematically rigorous derivation of the popular formula used to determine the SNR limitation introduced by the random occurrence of the sampling clock edge. Given a sinusoidal input of amplitude  $A_{\rm IN}$  and angular frequency  $\omega_{\rm IN}$  ( $\omega_{\rm IN} = 2\pi f_{\rm IN}$ )

$$V_{IN}(t) = A_{IN} \sin(\omega_{IN}t)$$

(11)

the jitter affecting the sampling clock cycle (expressed via the RMS timing error  $\sigma_T$ ) induces a theoretical RMS voltage error  $\sigma_{V \, jitter}$  dependent on the input waveform slope, and calculated by means of the formula

$$\sigma_{V \text{ jitter}} = \sigma_T \cdot \left| \frac{dV_{\text{IN}}(t)}{dt} \right| = \sigma_T \cdot A_{\text{IN}} \omega_{\text{IN}} \cdot |\cos(\omega_{\text{IN}} t)|.$$

(12)

Equation (12) translates into math the intuitive concept that little or no error is introduced by a jittery sampling instant when the input sinusoid is sampled at its peak, but uncertainty in the aperture time causes substantial noise in the sampled voltage when the input sinusoid is close to zero-crossing. Let us now consider the voltage noise stochastic process  $n_{V \text{ jitter}}$  engendered by the uncertainty  $\sigma_T$  affecting the sampling instants of  $V_{\text{IN}}(t)$ . Its power can be computed as

$$\sigma_{V\,\text{jitter}}^2 = \left\langle n_{V\,\text{jitter}}^2 \right\rangle = \int_{-A_{\text{IN}}}^{+A_{\text{IN}}} n_{V\,\text{jitter}}^2 \cdot \text{pdf}(V_{\text{IN}}) \, dV_{\text{IN}}$$

(13)

according to the most general definition of variance as *ensemble* average. In (13) the effective noise power is weighted by the

#### IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 6, JUNE 2005

probability density function  $pdf(V_{IN})$ , accounting for the probability of the noise having a specific value. The expression is then integrated over the whole range of possible noisy voltages (the input peak-to-peak). The procedure is analogous to the well-known calculation of the quantization noise  $\langle n_q^2 \rangle = q^2/12$  for a quantization cell of width q with uniform distribution.

For the single-tone tests universally adopted to assess the ADC performance, the weight function is the pdf of a sinusoid. The probability of the input voltage being at level  $V_{IN}$  is given by the familiar "bathtub" expression (see for instance [24])

$$pdf(V_{IN}) = \frac{1}{A_{IN}\pi\sqrt{1 - \left(\frac{V_{IN}}{A_{IN}}\right)^2}}.$$

(14)

The equation for  $n_{V\,\rm jitter}$  as a function of time t is formally identical to (12)

$$u_{V \text{ jitter}}(t) = n_T(t) \cdot \left| \frac{dV_{\text{IN}}(t)}{dt} \right|$$

=  $n_T(t) \cdot A_{\text{IN}}\omega_{\text{IN}} \cdot \cos(\omega_{\text{IN}}t).$  (15)

Hence, by combining (13) and (14) it can be written

$$\begin{split} &\tilde{V}_{V \text{ jitter}}^{\tilde{V} \text{ jitter}} \\ &= \left\langle n_{V \text{ jitter}}^{2}(t) \right\rangle = \int_{-A_{\text{IN}}}^{+A_{\text{IN}}} [n_{T}(t) \cdot A_{\text{IN}} \omega_{\text{IN}} \cdot \cos(\omega_{\text{IN}} t)]^{2} \\ &\cdot \frac{1}{A_{\text{IN}} \pi \sqrt{1 - \left(\frac{V_{\text{IN}}}{A_{\text{IN}}}\right)^{2}}} \, dV_{\text{IN}} \\ &= \left\langle n_{T}^{2}(t) \right\rangle \cdot (A_{\text{IN}} \omega_{\text{IN}})^{2} \cdot \int_{-A_{\text{IN}}}^{+A_{\text{IN}}} \cos^{2}(\omega_{\text{IN}} t) \\ &\cdot \frac{1}{\pi \sqrt{1 - \left(\frac{V_{\text{IN}}}{A_{\text{IN}}}\right)^{2}}} \frac{dV_{\text{IN}}}{A_{\text{IN}}}. \end{split}$$

(16)

The ensemble average of the clock jitter process  $n_T(t)$  is  $\sigma_T^2$ , and can be taken out of the integral as long as the clock edge uncertainty is independent from the input amplitude, as is commonly postulated. In reality, to a degree the MOSFET sampling switch will introduce deviations from this idealized behavior. The variable t is now to be expressed in terms of the voltage  $V_{\rm IN}$ . From (11), it is

$$\omega_{\rm IN}t = \arcsin\left(\frac{V_{\rm IN}}{A_{\rm IN}}\right). \tag{17}$$

Therefore, as needed in order to rewrite (16)

$$\cos(\omega_{\rm IN}t) = \cos\left(\arcsin\left(\frac{V_{\rm IN}}{A_{\rm IN}}\right)\right) \tag{18}$$

where the latter is a measure of the sensitivity of a sample taken from a sinusoidal input, to the aperture jitter affecting the SHA clock edge. Not surprisingly, (14) along with (18) highlight how the input roams the most where the jitter is less of a problem. Finally, substituting  $x=V_{\rm IN}/A_{\rm IN}$  for sake of simplicity, the expression in (16) becomes

$$\sigma_{V\,\text{jitter}}^2 = (\sigma_T \cdot A_{\text{IN}}\omega_{\text{IN}})^2 \\ \cdot \int_{-1}^{+1} \cos^2(\arcsin(x)) \cdot \frac{1}{\pi\sqrt{1-x^2}} \, dx \quad (19)$$

where the second member can be easily calculated with Maple and is indeed equal to 1/2. Considering that the probe tone power is given by  $A_{\rm IN}^2/2$ , (8) for the  ${\rm SNR}_{\rm jitter}$  is finally derived.

In conclusion, the rigorous statistical calculation justifies the well-known formula linking SNR to the clock jitter in absence of other noise additions, which had been formerly devised in [17] on a more heuristic basis.

4

[17] M. Shinagawa, Y. Akazawa, and T. Wakimoto, "Jitter analysis of highspeed sampling systems," *IEEE J. Solid-State Circuits*, vol. 25, no. 1, pp. 220–224, Feb. 1990.

Let  $x(t) = \frac{1}{2}A_{FS}\sin(2\pi f_i t)$  and  $\Delta t$  be a random variable, then

$$\begin{split} x(k) &= x \left( kT_s + \Delta t \right) \approx \frac{1}{2} A_{FS} \sin(2\pi f_i kT_s) + \frac{dx(t)}{dt} \bigg|_{t=kT_s} \times \Delta t \\ &\approx \frac{1}{2} A_{FS} \sin(2\pi f_i kT_s) + A_{FS} \pi f_i \cos(2\pi f_i kT_s) \times \Delta t \\ &\overline{x^2(k)} = \frac{1}{8} A_{FS}^2 + \frac{1}{2} A_{FS}^2 \pi^2 f_i^2 \times \overline{\Delta t^2} = P_s + P_n \end{split}$$

The signal-to-noise ratio of X(k) is

$$SNR = \frac{P_s}{P_n} = \frac{1}{4\pi^2 f_i^2 \cdot \overline{\Delta t^2}} = -20 \log \left(2\pi f_i \cdot \Delta t_{\rm rms}\right) \, dB$$

### Little Known Characteristics of Phase Noise by Paul Smith

#### by

#### PHASE JITTER IN SAMPLED DATA SYSTEMS

The easiest way to calculate the SNR degradations incurred by phase noise in a sampled data system is to convert phase noise to phase jitter. This is most easily accomplished by recognizing that a time delay is the same as a phase delay at a given frequency. Extending this concept and writing it in terms of noise power yields Equation 1.

$$\sigma_{\theta}^{2} = \omega_{olk}^{2} \sigma_{t}^{2},$$

where  $\sigma_{\theta} = phase \ noise \ in \ rms \ radians$

$$\sigma_{t} = phase \ jitter \ in \ rms \ seconds$$

$$\omega_{olk} = clock \ frequency \ in \ radians/sec$$

(1)

That is, for a given jitter error, a higher frequency signal will have more phase error. The term  $\sigma_{\theta}$  is the total integrated phase noise of the clock<sup>4</sup> and defines the clock SNR by

$$SNR_{ac}(dB) = -10 \log(\sigma_a^2)$$

(2)

Thus, Equation 1 relates the total integrated phase noise, or clock SNR, to the total jitter in the clock. Phase noise and clock jitter are two different ways to look at the same phenomenon.

#### Figure 1.

Traditional sampled data SNR analyses use Figure 1 as an aid to determine how noise on a clock generates an error in the sampled data. From this it is seen that

$$\Delta v(t) = \Delta t \times v'_{out}(t)$$

$$E \left\{ \Delta v^{2}(t) \right\} = E \left\{ \Delta t^{2} \times v'_{out}^{2}(t) \right\}$$

$$E \left\{ \Delta v^{2}(t) \right\} = E \left\{ \Delta t^{2} \right\} \times E \left\{ v'_{out}^{2}(t) \right\}$$

Therefore,

$$\begin{split} \sigma_{err}^2 &= \sigma_t^2 \times E \Big\{ {v'}_{out}^2(t) \Big\}, \\ \text{where } \sigma_t^2 \text{ is in} \big( \text{rms seconds} \big)^2 \end{split}$$

From this it is seen that the noise power is a function of the jitter power and the power in the signal derivative.

The SNR of a signal sampled with a jittery clock is defined as

$$SNR_{stg} = \frac{\text{power in signal}}{\text{power in noise}} = \frac{\sigma_{out}^2}{\sigma_{or}^2} = \frac{1}{\sigma_t^2} \frac{E\left\{v_{out}^2(t)\right\}}{E\left\{v_{out}^2(t)\right\}}$$

(3)

For example, in a single sine wave,

A2

$$v_{out}(t) = A \sin \omega_0 t$$

$v'_{out}(t) = A \omega_0 \cos \omega_0 t$

Therefore,

$$E\left\{v_{out}^{2}(t)\right\} = \text{power in } v_{out}(t) = \frac{A^{2}}{2}$$

$$E\left\{v_{out}^{2}(t)\right\} = \text{power in } v_{out}'(t) = \frac{\omega_{O}^{2}A^{2}}{2}$$

Using Equation 3,

$$SNH_{syr} = \frac{1}{\sigma_t^2} \frac{\frac{\sigma}{2}}{\frac{\omega_o^2 A^2}{2}} = \frac{1}{\sigma_t^2} \frac{1}{\omega_o^2}$$

(4a)

$$SNR_{sig} = \frac{1}{4\pi^2 f_0^2 \sigma_t^2}$$

, for a single carrier system. (4b)

This is the standard SNR equation for a single sine wave sampled by a clock with jitter and can be found in many publications<sup>5</sup>. Intuitively what is happening is that higher frequency signals have larger slew rates. This results in larger voltage changes as the sample time changes. It should be remembered that quantization noise and thermal noise must also be added to this to obtain the total noise out of a data converter.

<sup>4</sup>"VCO Phase Noise," Mini-Circuits, Application Note #2.

<sup>5</sup>"Linear Design Seminar," Analog Devices, Inc., Norwood, MA, 1995, pp. 5-20.

. . . . .

# Effect of Jitter on Asynchronous Sampling With Finite Number of Samples

Nicola Da Dalt, Member, IEEE

Usually, the jitter requirements of the frequency synthesizers that provide the sampling clock to the ADC is determined at system level by using the following expression for sinusoidal signals

$$SNR = 20 \log_{10} \left( \frac{1}{2\pi f_{sig} \cdot \sigma_{tj}} \right) \tag{1}$$

or its extension valid for any kind of signal [1]

$$SNR = 10 \log_{10} \left( \frac{r_x(0)}{-r''_x(0) \cdot \sigma_{\rm tj}^2} \right)$$

(2)

where x is the analog signal to be sampled (assumed to be wide sense stationary and with zero mean),  $r_x$  is its autocorrelation function (the prime denotes the derivative) and  $\sigma_{tj}$  is the long term jitter (as defined in [1]) divided by  $\sqrt{2}$ . This expression is derived from statistical considerations, assuming the evaluation of the SNR is performed on an infinite number of samples.

> N. Da Dalt, M. Harteneck, C. Sandner, and A. Wiesbauer, "On the jitter requirements of the sampling clock for analog to digital converters," *IEEE Trans. Circuits Syst. I*, vol. 49, pp. 1354–1360, Sept. 2002.

#### A. Sinusoidal Input

As application of the relationship (3), the SNR in case of sinusoidal input is calculated. Assuming  $x(t) = A \cdot \sin(\omega t)$ , the autocorrelation function is

$$r_x(mT) = \frac{A^2}{2}\cos(\omega mT)$$

and the second derivative is

$$r_x''(mT) = \frac{-\omega^2 A^2}{2} \cos(\omega mT)$$

By substitution in (5), it is easy to find the well-known formula [ for the aperture jitter SNR in sampling of sinusoidal signals

$$\text{SNR} = 20 \cdot \log_{10} \left(\frac{1}{\omega \sigma_{tj}}\right) \text{dB}$$

6

Jitter is critical in high-performance data converters

- <u>0.3ps</u> rms can be considered as "bad" for ADS55XX

- ADC applications require 2-3 orders of magnitude better jitter than high-speed digital applications

# Jitter noise can exceed quantization noise

- Quantization noise of an N-bit ADC SNRmax<sub>auantization</sub> = 6.02\*N+1.76

- Jitter noise of an N-bit ADC

SNR max <sub>jitter</sub> = -20 log(2πfε)

- Find 'quantization noise equivalent' jitter

$$\varepsilon < \frac{1}{2\pi f \, 10^{0.3N}},$$

$f = input \ frequency$

$$\varepsilon = rms \_ jitter$$

# Jitter Tolerance of Nyquist ADCs (ps rms)

| Fin    | 8bit  | 10bit | 12bit | 14bit | 16bit | 18bit | 20bit | 22bit | 24bit |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 10KHz  | 64512 | 16128 | 4032  | 1008  | 252   | 63    | 16    | 4     | 1     |

| 100KHz | 6451  | 1612  | 403   | 101   | 25.2  | 6.3   | 1.6   | 0.4   | 0.1   |

| 1MHz   | 645   | 161   | 40.3  | 10.1  | 2.52  | 0.63  | 0.16  | 0.04  | 0.01  |

| 10MHz  | 64    | 16.1  | 4.03  | 1.01  | 0.252 | 0.06  | 0.01  | 0.00  | 0.00  |

| 100MHz | 6.4   | 1.61  | 0.40  | 0.10  | 0.025 | 0.006 | 0.00  | 0.00  | 0.00  |

[ T. Kuyel, 2005 ]