| Data Converters for Telecom |              |            |                        |         |                       |                                                                                |                         |            |

|-----------------------------|--------------|------------|------------------------|---------|-----------------------|--------------------------------------------------------------------------------|-------------------------|------------|

| Application                 | Year         | Supply     | Technology             | Bits    | fs<br>OSR             | Туре                                                                           | Area<br>mm <sup>2</sup> | Powe<br>mW |

| Speech                      | 1980<br>1985 | ±5V<br>±5V | 5 μ NMOS<br>2.4 μ CMOS | 8<br>12 | 8 kHz<br>1 MHz        | Suc. Appro A/D<br>2 <sup>nd</sup> Order ΣΔ A/D                                 | 3.5                     | 50<br>20   |

|                             | 1990         | +5 V       | 1.2 μ CMOS             | 13      | 256x<br>2 MHz<br>512x | $\Sigma \Delta D/A$<br>$2^{nd} Order \Sigma \Delta A/D$<br>$\Sigma \Delta D/A$ | 2 2 1                   | 6          |

|                             | 1995         | +5 V       | 0.7 μ CMOS             | 14      | 2 MHz<br>512x         | $2^{nd}$ Order $\sum \Delta A/D$<br>$\sum \Delta D/A$                          | 1.5<br>2                | 5<br>3     |

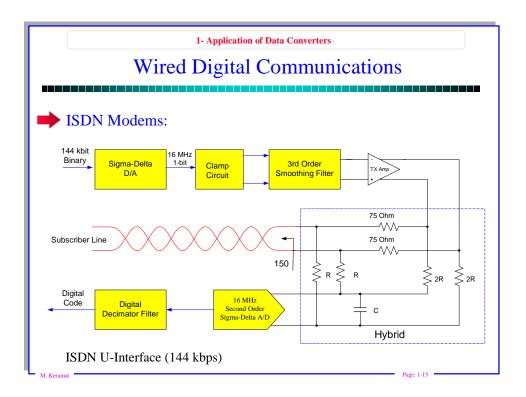

| ISDN                        | 1987         | +5 V       | 2 μ CMOS               | 10      | 16 MHz<br>128x        | $2^{nd} \operatorname{Order} \sum \Delta A/D \over \sum \Delta D/A$            | 2                       | 15         |

|                             | 1996         | + 3 V      | 0.5 μ CMOS             | 10      | 16 MHz<br>128x        | $4^{th} \text{ order } \sum D A/D \\ 6^{th} \text{ order } \sum D D/A$         | 2<br>1.5                | 35<br>10   |

| GSM                         | 1990         | +5 V       | 1.2 μ CMOS             | 8       | 270 kHz<br>1 x        | Suc. Appr. A/D<br>Binary Weig D/A                                              | 1                       | 10         |

|                             | 1993         | +5 V       | 0.7 μ CMOS             | 8       | 270 kHz<br>1 x        | Suc. Appr. A/D<br>Binary Weig D/A                                              | 1                       | 10         |

|                             | 1995         | + 3 V      | 0.5 μ CMOS             | 13<br>8 | 6.5 MHz<br>24x        | 4 <sup>th</sup> order ∑D A/D<br>BinWeig. D/A                                   | 1.5<br>0.4              | 14<br>3    |

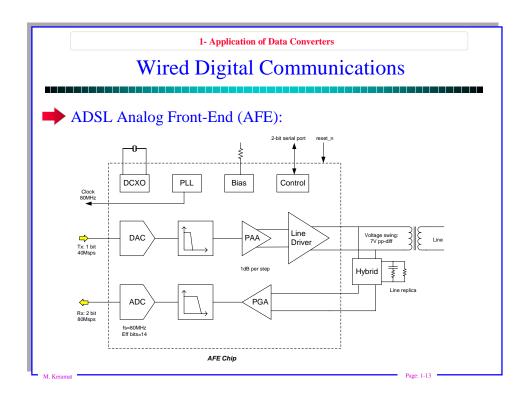

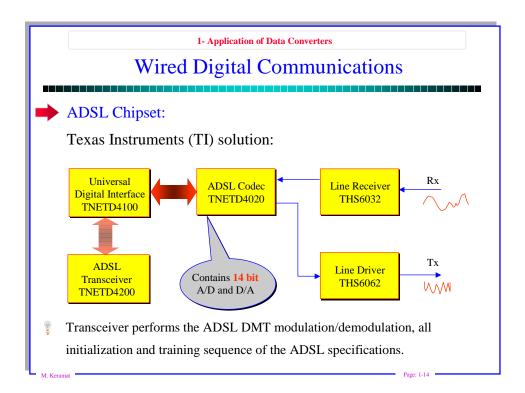

| ADSL                        | 1993         | +5 V       | 0.7 μ CMOS             | 12      | 53 MHz<br>24x         | $4^{th} \text{ order } \sum D A/D  6^{th} \text{ order } \sum D D/A$           | 9<br>7                  | 850<br>700 |

|                             | 1997         | +3V        | 0.5 μ CMOS             | 12      | 8.8 MHz<br>4x         | Pipelined A/D<br>Switched-I D/A                                                | 5<br>2                  | 120<br>30  |

| VDSL                        | 1998         | +3 V       | 0.35 µ CMOS            | 12      | 40 M H z<br>1 x       | Pipelined A/D<br>Switched-I D/A                                                | 5<br>2                  | 250<br>60  |